ARM Architecture

May 4, 2020 | by Kishore Kumar Boddu

ARM cores are designed specifically for embedded systems. The needs of embedded systems can be satisfied only if features of RISC and CISC are considered together for processor design. So ARM architecture is not a pure RISC architecture. It has a blend of both RISC and CISC features.

ARM Architecture Features and Benefits:

| Features | Benefits to embedded system |

| High Performance | Ensures the system has a fast response |

| Low power consumption | Makes the system more energy efficient |

| Low silicon area | Reduces the size and also consumes less power |

| High Code density | Helps embedded system to have less memory footprint |

| Load/store architecture | Used to load data from the memory to the ARM CPU register or store data from the CPU register to the memory; enables the memory access when required |

| Register bank with large number of working registers | Required to perform most of the operations within the CPU and provides faster context switch in a multitasking applications |

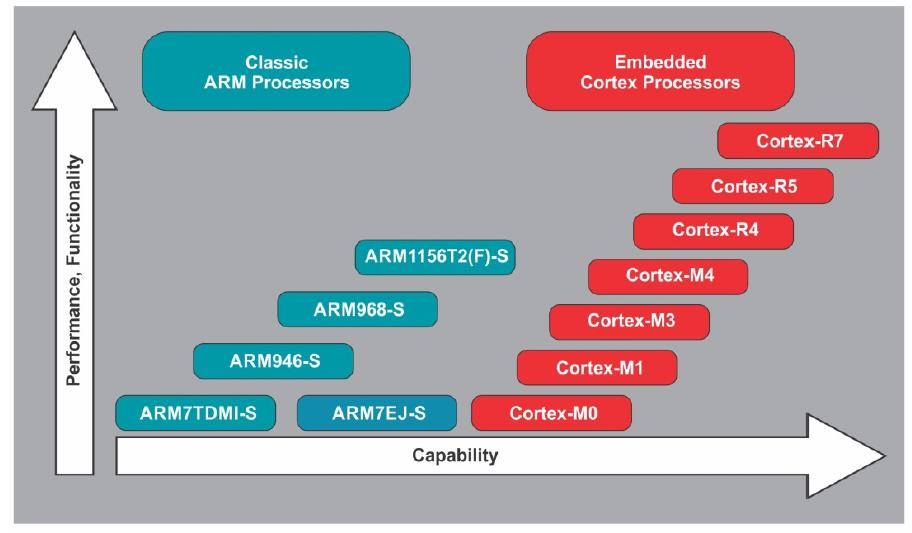

In the path of architectural evolution, ARM has contributed many versions of IP cores to the embedded computing world. ARM pioneered embedded products are excelling in every visible spectrum. Since its inception, ARM has migrated over a long meaningful road map starting from v4T ARM7TDMI to v7 Cortex series of architectures achieving many strong milestones in between. It is currently the new era of feature rich ARM Cortex series architectures truly empowering the embedded computing world.

ARM architecture evolution:

ARM architecture v7 profile:

In order to provide a wide coverage of different application domains, addressing their specific requirements, ARM core is evolved into architecture version7 which has three different profiles: the application profile, real time profile and microcontroller profile. Architecture v7 should not be confused with ARM7 which has been explained before under architecture v4.

Application profile (Cortex -A)

Cortex A series of architectures are multicores with power efficiency and high performance. Every Cortex – A implementation is intended for highest performance at ultralow power design. It supports with, in-built memory management unit. Being influenced by multitasking OS system requirements, it has virtualization extensions and provides a trust zone for a safe and extensible system. It has enhanced Java support and provides a secure program execution environment. These architectures are typically designed for high end real time safety critical applications like automotive powertrain system. Some Cortex- A application products are smart phones, tablets, televisions and even high end computing servers.

Real-time profile (Cortex -R)

Cortex R series of architectures are designed for deeply embedded real time multitasking applications. They have low interrupt latency and predictability features for real time needs. It provides memory protection for supervisory OS tasks being in privileged mode. It also provides tightly coupled memories for fast deterministic access. Typical application examples are: hard disk drive controller and base band controller for mobile applications and engine management unit where high performance and reliability at very low interrupt latency and determinism are critical requirements.

Microcontroller profile (Cortex -M)

Cortex M series of architectures have v6-M as cortex M0, M0+ and M1 and v7-M with Cortex M3, M4 and other successors. This series of architectures developed for deeply embedded microcontroller profile, offer lowest gate count so smallest silicon area. These are flexible and powerful designs with completely predictable and deterministic interrupt handling capabilities by introducing the nested vector interrupt controller (NVIC). The small instruction sets support for high code density and simplified software development. Developers are able to achieve 32-bit performance at 8-bit price. The very low gate count of Cortex M0 facilitates its deployment in analog and mixed mode devices. Due to further demanding applications requiring even better energy efficiency, Cortex M0+ was designed with two stage pipeline and achieved high performance with very low dynamic power consumption, reduced branch shadow and reduced number of flash memory access. Cortex M1 was designed for implementation in FPGA. It is functionally a subset of Cortex M3 and runs ARM v6 instruction set with OS extension options. It has 32-bit AHB lite bus interface, separate tightly coupled memory interface and JTAG interface to facilitate debug options. It has three stage pipeline implementation and configurable NVIC for reducing interrupt latency.

Cortex M4 Features:

- Thumb2 instruction set delivers the significant benefits of high code density of Thumb with

- 32-bit performance of ARM.

- Optional IEEE754-compliant single-precision Floating Point Unit.

- Code-patch ability for memory system updates.

- Power control optimization by integrating sleep and deep sleep modes.

- Hardware division and fast multiply and accumulate for SIMD DSP instructions.

- Saturating arithmetic for noise cancellation in signal processing.

- Deterministic, low latency interrupt handling for real time-critical applications.

- Optional Memory Protection Unit(MPU) for safety-critical applications

- Extensive implementation of debug, trace and code profiling capabilities.

ARM Cortex M Programming Model:

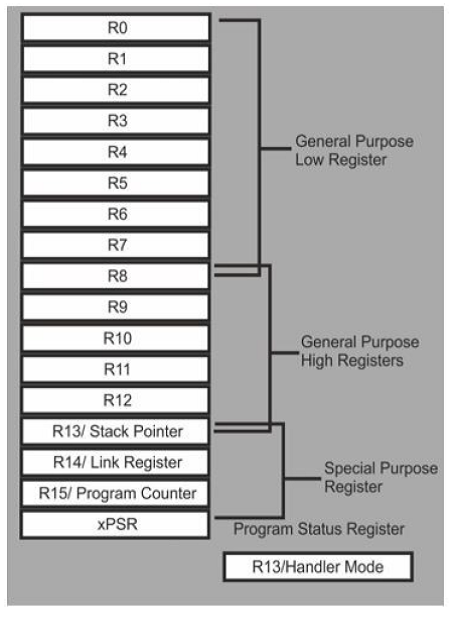

The programming model of the Cortex-M4 processors has 18 working registers shown in below Figure. Thirteen of them are general purpose 32-bit registers, three have special uses and two stack pointers.

Leave Your Comment