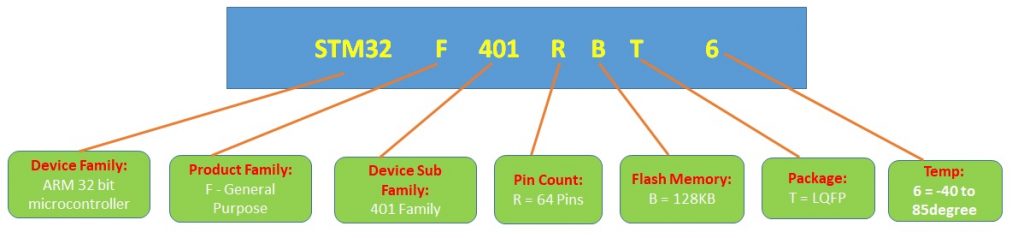

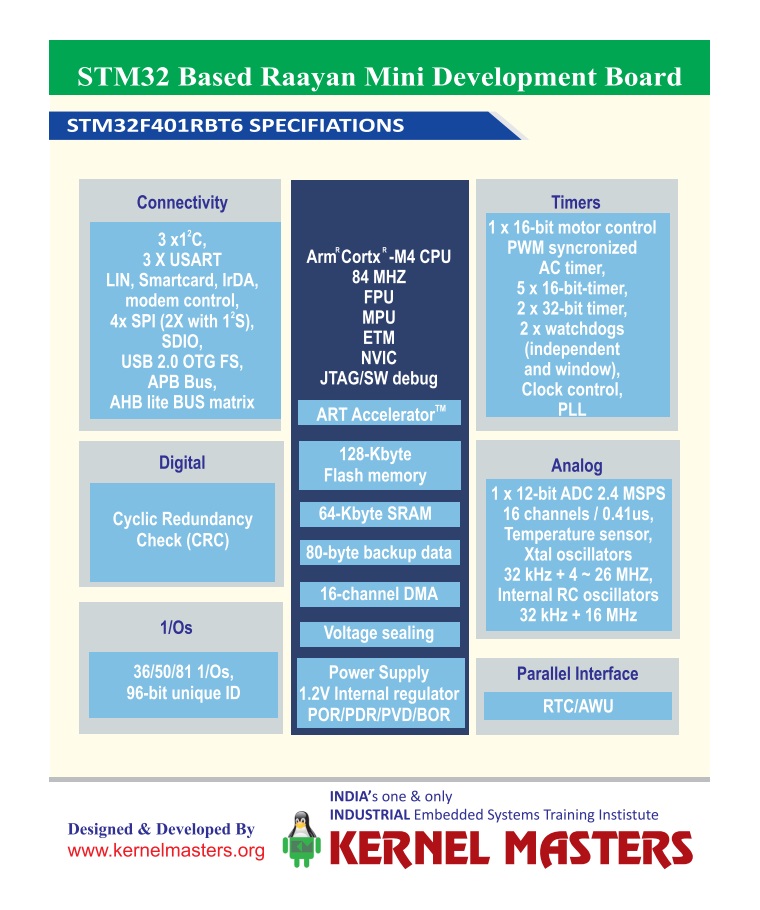

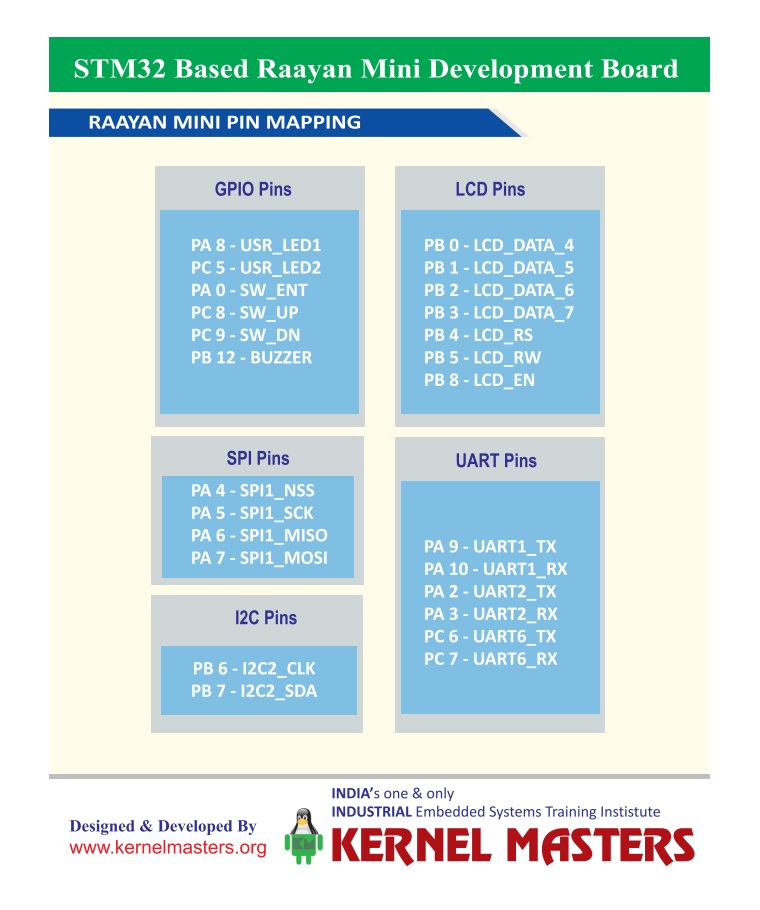

STM32F401RBT6 Micro Controller

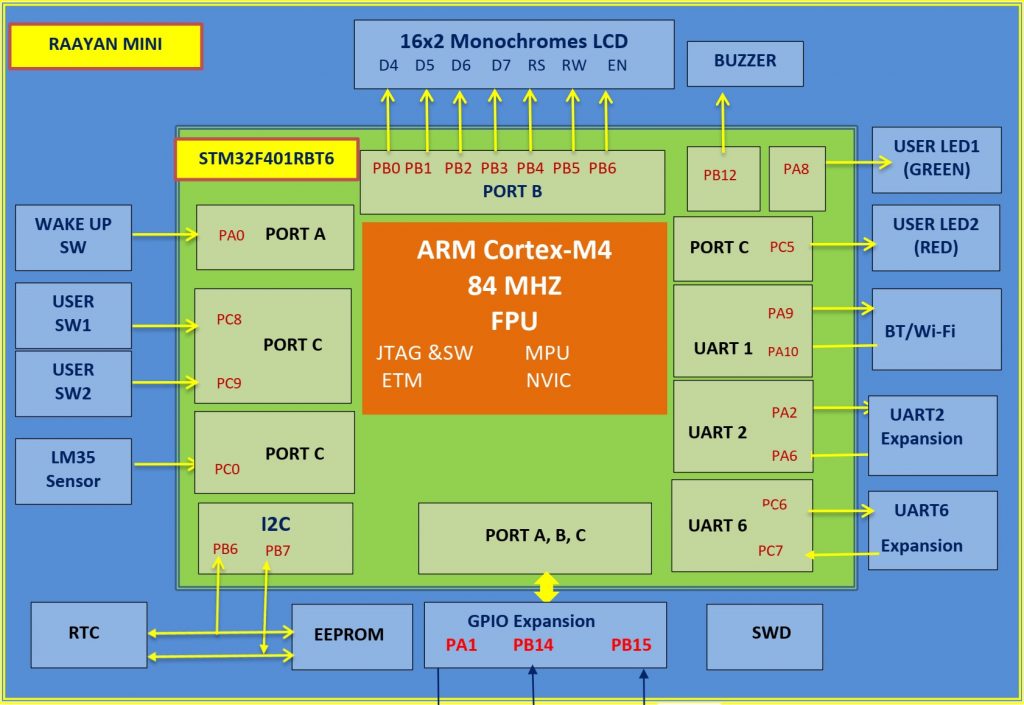

Raayan Mini Board Block Diagram:

| Linux Kernel Programming | Linux Device Drivers |

| Kernel Developers focus on interfaces, data structures, algorithms and optimization for the core of the operating system. | Device Drivers use the interfaces and data structures written by the kernel developers to implement device control and IO. |

| Kernel programming is done using Module programming technique.There are no standard libraries available. Have to use pure C programming. | Device Drivers is done using Module programming technique.There are no standard libraries available. Have to use pure C programming. |

| A very good kernel programmer may not know a lot about interrupt latency and hardware determinism, but he will know a lot about how locks, queues and Kobjects work. | A device driver programmer will know how to use locks, queues and other kernel interfaces to get their hardware working properly and responsively, but he won’t be as likely to fix a page allocation bug or write a new scheduler. |

Buy a Community development board and apply the C programming skill to do good electronic projects by yourself without copying a single line of code from net/book/friends.

ARM cores are designed specifically for embedded systems. The needs of embedded systems can be satisfied only if features of RISC and CISC are considered together for processor design. So ARM architecture is not a pure RISC architecture. It has a blend of both RISC and CISC features.

| Features | Benefits to embedded system |

| High Performance | Ensures the system has a fast response |

| Low power consumption | Makes the system more energy efficient |

| Low silicon area | Reduces the size and also consumes less power |

| High Code density | Helps embedded system to have less memory footprint |

| Load/store architecture | Used to load data from the memory to the ARM CPU register or store data from the CPU register to the memory; enables the memory access when required |

| Register bank with large number of working registers |

Required to perform most of the operations within the CPU and provides faster context switch in a multitasking applications |

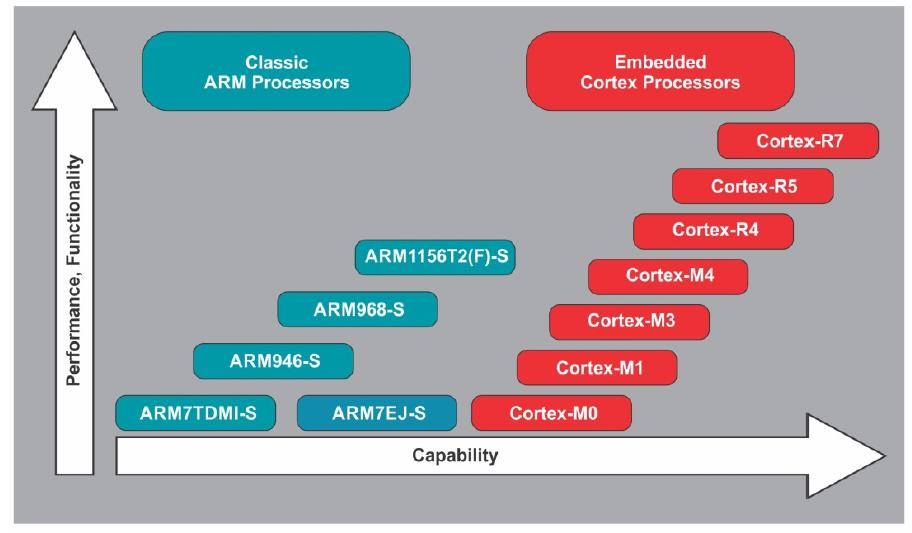

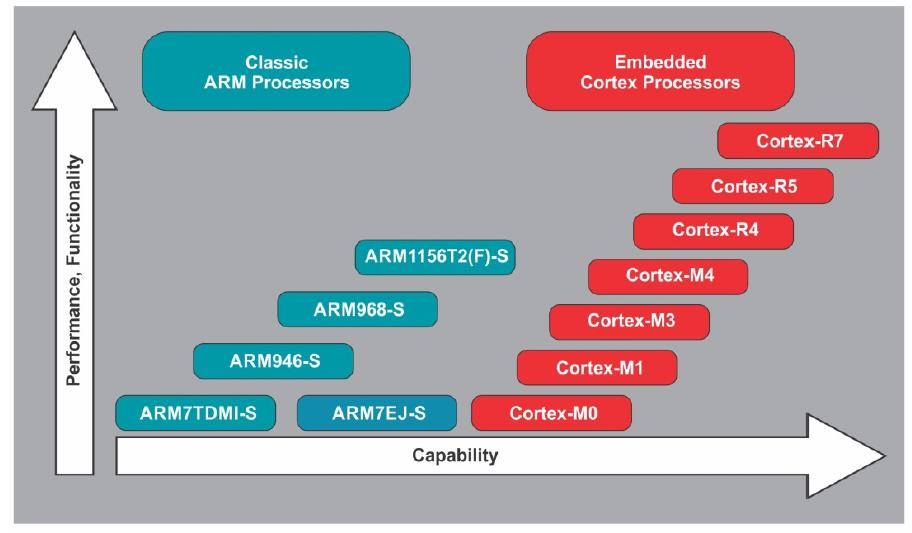

In the path of architectural evolution, ARM has contributed many versions of IP cores to the embedded computing world. ARM pioneered embedded products are excelling in every visible spectrum. Since its inception, ARM has migrated over a long meaningful road map starting from v4T ARM7TDMI to v7 Cortex series of architectures achieving many strong milestones in between. It is currently the new era of feature rich ARM Cortex series architectures truly empowering the embedded computing world.

In order to provide a wide coverage of different application domains, addressing their specific requirements, ARM core is evolved into architecture version7 which has three different profiles: the application profile, real time profile and microcontroller profile. Architecture v7 should not be confused with ARM7 which has been explained before under architecture v4.

Cortex A series of architectures are multicores with power efficiency and high performance. Every Cortex – A implementation is intended for highest performance at ultralow power design. It supports with, in-built memory management unit. Being influenced by multitasking OS system requirements, it has virtualization extensions and provides a trust zone for a safe and extensible system. It has enhanced Java support and provides a secure program execution environment. These architectures are typically designed for high end real time safety critical applications like automotive powertrain system. Some Cortex- A application products are smart phones, tablets, televisions and even high end computing servers.

Cortex R series of architectures are designed for deeply embedded real time multitasking applications. They have low interrupt latency and predictability features for real time needs. It provides memory protection for supervisory OS tasks being in privileged mode. It also provides tightly coupled memories for fast deterministic access. Typical application examples are: hard disk drive controller and base band controller for mobile applications and engine management unit where high performance and reliability at very low interrupt latency and determinism are critical requirements.

Cortex M series of architectures have v6-M as cortex M0, M0+ and M1 and v7-M with Cortex M3, M4 and other successors. This series of architectures developed for deeply embedded microcontroller profile, offer lowest gate count so smallest silicon area. These are flexible and powerful designs with completely predictable and deterministic interrupt handling capabilities by introducing the nested vector interrupt controller (NVIC). The small instruction sets support for high code density and simplified software development. Developers are able to achieve 32-bit performance at 8-bit price. The very low gate count of Cortex M0 facilitates its deployment in analog and mixed mode devices. Due to further demanding applications requiring even better energy efficiency, Cortex M0+ was designed with two stage pipeline and achieved high performance with very low dynamic power consumption, reduced branch shadow and reduced number of flash memory access. Cortex M1 was designed for implementation in FPGA. It is functionally a subset of Cortex M3 and runs ARM v6 instruction set with OS extension options. It has 32-bit AHB lite bus interface, separate tightly coupled memory interface and JTAG interface to facilitate debug options. It has three stage pipeline implementation and configurable NVIC for reducing interrupt latency.

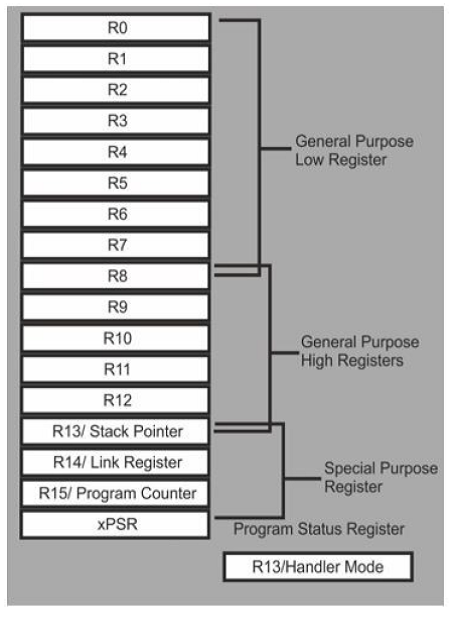

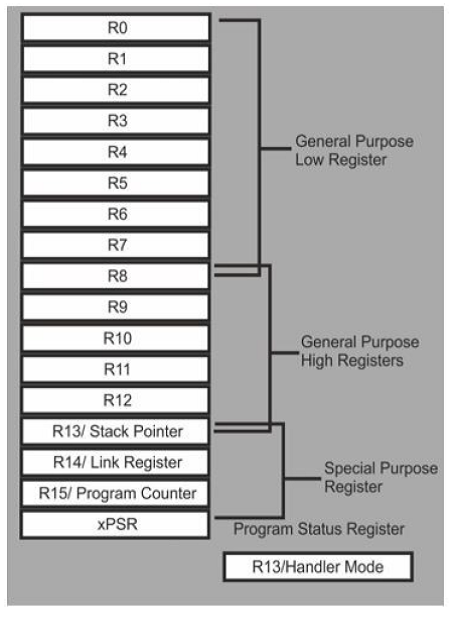

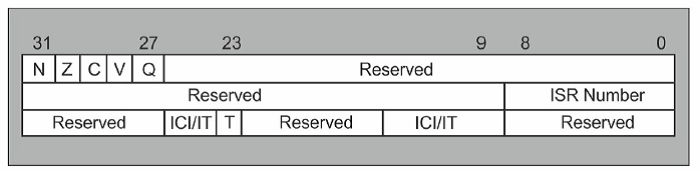

The programming model of the Cortex-M4 processors has 18 working registers shown in below Figure. Thirteen of them are general purpose 32-bit registers, three have special uses and two stack pointers.

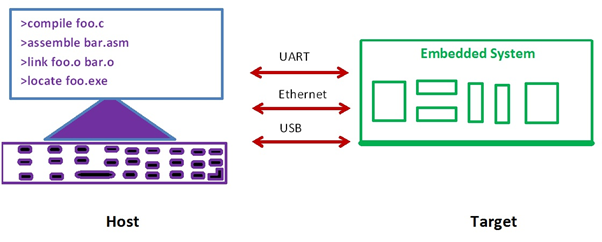

Embedded software build process is a transformation performed by software running on a general purpose computer.

The compiler, assembler, linker and locator are all pieces of software that run on a host computer, rather than on the embedded system itself. Finally executable image run on a target embedded system.

Host (Development) machine communicate to the target various types of interfaces like UART, Ethernet and USB.

| CISC | RISC |

| Many complex instructions | Simple instructions, few in Number, Few addressing modes |

| Variable length instructions | Fixed length instructions |

| Many instructions can access memory | Only LOAD/STORE instructions access memory |

| mov ax, 10 mov bx, 5 mul bx, ax |

mov ax, 0 mov bx, 10 mov cx, 5 Begin add ax, bx loop Begin |

| The total clock cycles for the CISC version might be: (2 movs × 1 cycle) + (1 mul × 30 cycles) = 32 cycles |

While the clock cycles for the RISC version is: (3 movs × 1 cycle) + (5 adds × 1 cycle) + (5 loops × 1 cycle) = 13 cycles |

| Example: x86 ISA | Examples: ARM, MIPS, PowerPC (IBM), SPARC (Sun) |

| Little Endian | Big Endian |

| “Little Endian” means that the lower-order byte of the number is stored in memory at the lowest address, and the high-order byte at the highest address. | “Big Endian” means that the high-order byte of the number is stored in memory at the lowest address, and the low-order byte at the highest address. |

| For example, a 4 byte Integer Byte3 Byte2 Byte1 Byte0 will be arranged in memory as follows: Base Address+0 Byte0 Base Address+1 Byte1 Base Address+2 Byte2 Base Address+3 Byte3 |

The same 4 byte integer would be stored as: Base Address+0 Byte3 Base Address+1 Byte2 Base Address+2 Byte1 Base Address+3 Byte0 |

| Intel processors (those used in PC’s) use “Little Endian” byte order. | ARM processors (those used in PC’s) use “Big Endian” byte order. |

| I/O Mapped I/O | Memory Mapped I/O |

| Separate address bus for I/O and memory. | Common address bus for I/O and Memory. |

| Support IN and OUT Assembly Instructions. | There are no separate IN & OUT instructions. What are the instructions are to communicate memory same instructions useful to communicate I/O. |

| Separate control lines for I/O. IOR and IOW | No separate control Lines for I/O. Memory control lines only MEMR, MEMW. |

| Register Plus Memory | Load Store Architecture |

| Allows operations to be performed on (or from) memory, as well as registers. If the architecture allows all operands to be in memory or in registers, or in combinations, it is called a “register plus memory” architecture. |

load/store architecture divides instructions into 2 categories: • Memory access (load and store between memory and registers). • ALU operations (which only occur between registers). |

| Example: ADD M ; A <- A + [M | Example: ADD r3,r2,r1 |

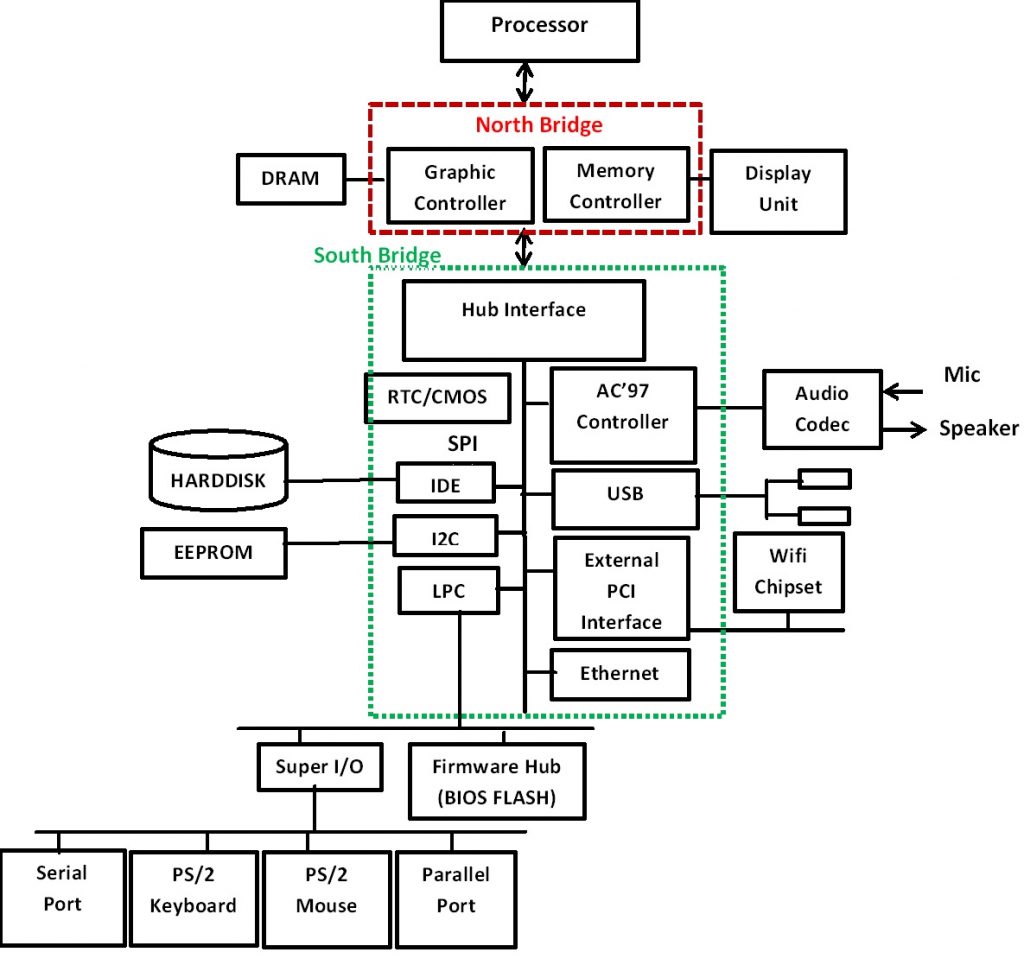

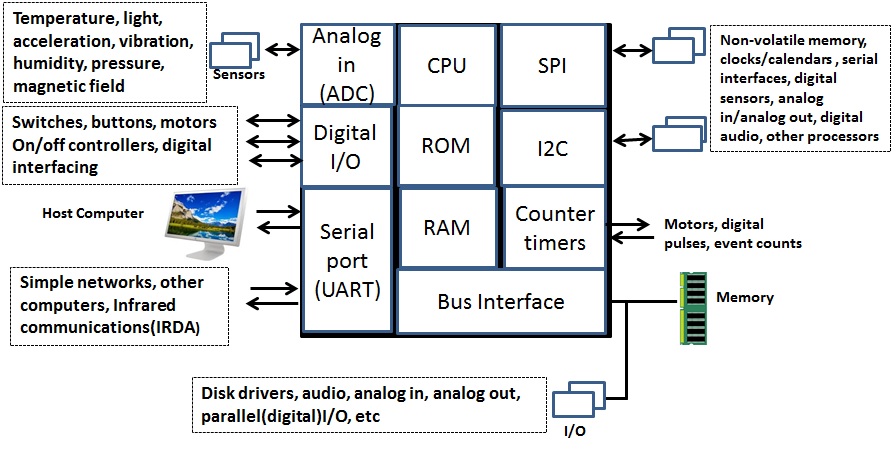

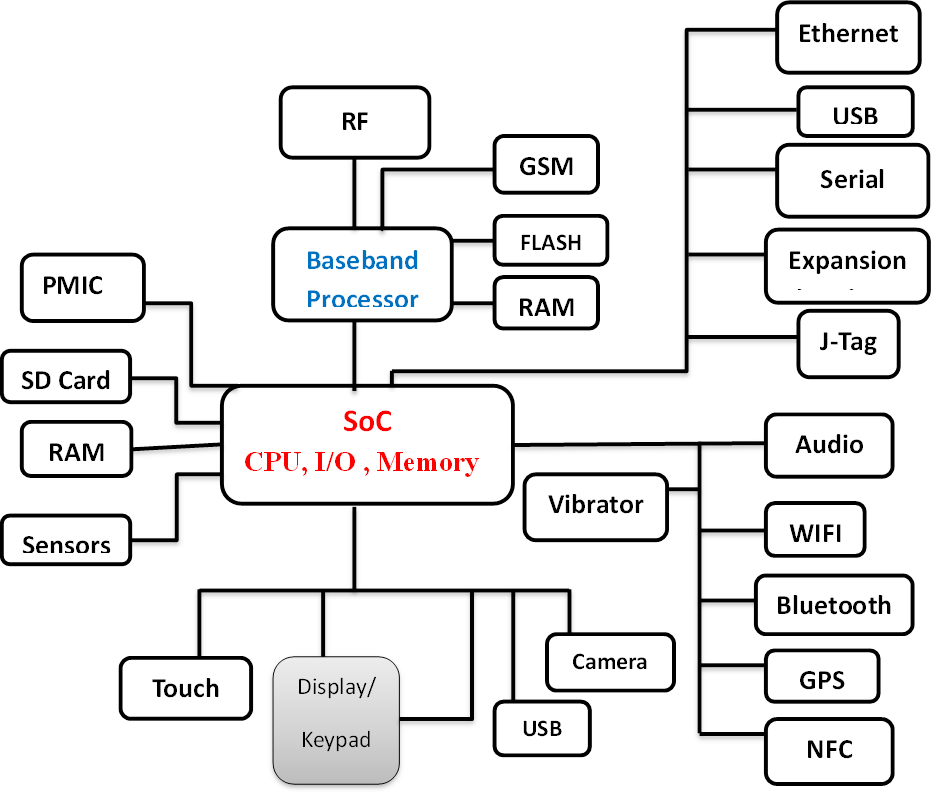

| Hardware Required | Desktop Computer | Simple Embedded Computer Ex: remote Controller |

Complex Embedded Computer Ex: Mobile Phone |

| Processor (Bus Width) |

High end processor 32 bit/ 64 bit Ex: Intel Processor |

Low End Processor 8 bit/16 bit Ex: 8051 (8 bit) ARM Cortex M4 |

High end processor 32 bit/ 64 bit Ex: ARM Cortex A9 |

| CISC or RISC | CISC | RISC | RISC |

| Caches and MMU | Yes | No | Yes |

| Memory | 2G to 64 GB | 32KB to 128 MB | 128 MB to 4GB |

| Multiprocessor | Supports Dual Core/ Quad Core/ Hexa Core | Doesn’t support Multicore | Supports Dual Core/ Quad Core/ Hexa Core |

| Sensors | Doesn’t Support Sensor interface | Support Sensors Interface | Support High end sensors interface |

| External Device Interface | Supports | Once Device manufactured, can’t interface new device to the target. | Once Device manufactured, can’t interface new device to the target. |

| Software Required | Desktop Computer | Simple Embedded Computer Ex: remote Controller |

Complex Embedded Computer Ex: Mobile Phone |

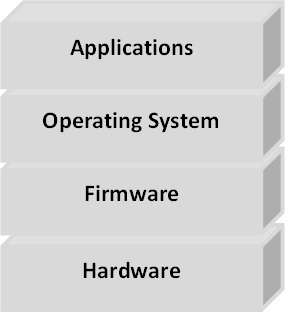

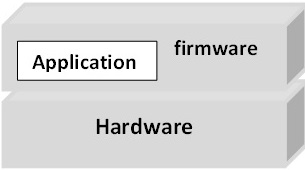

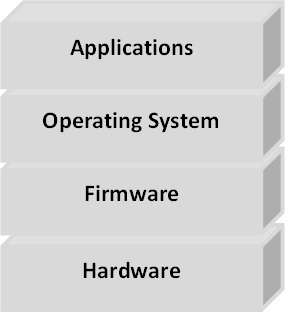

| Software layers in the Computer |  |

|

|

| Operating System | Windows/Linux | Doesn’t Support OS. | Supports Windows/Linux/Android |

| Firmware | BIOS | Whole system develops using firmware | Bootstrap program |

| Programming Languages | C/C++/Java/html/ php |

Assembly/C | Assembly/C/C++/Java/ html/php |

At the lowest level are programs that are run by the processor when the computer first powers up. These programs initialize the other hardware subsystems to a known state and configure the computer for correct operation. The software, because it is permanently stored in the computer’s memory, is known as firmware.

Above the firmware, the operating system controls the operation of the computer.

Firmware is software that is programmed into chips permanent/temporary and usually performs basic instructions, like BIOS, for various components, Network cards, and computer BIOS, etc…

Embedded C Programming is also called Firmware.

An operating system (OS) is system software that manages computer hardware and software resources and provides common services for computer programs.

Kernel is core part of the operating system. Kernel provides core service like Process management, Memory management, File management, Device and network services.

ARM cores are designed specifically for embedded systems. The needs of embedded systems can be satisfied only if features of RISC and CISC are considered together for processor design. So ARM architecture is not a pure RISC architecture. It has a blend of both RISC and CISC features.

| Features | Benefits to embedded system |

| High Performance | Ensures the system has a fast response |

| Low power consumption | Makes the system more energy efficient |

| Low silicon area | Reduces the size and also consumes less power |

| High Code density | Helps embedded system to have less memory footprint |

| Load/store architecture | Used to load data from the memory to the ARM CPU register or store data from the CPU register to the memory; enables the memory access when required |

| Register bank with large number of working registers |

Required to perform most of the operations within the CPU and provides faster context switch in a multitasking applications |

In the path of architectural evolution, ARM has contributed many versions of IP cores to the embedded computing world. ARM pioneered embedded products are excelling in every visible spectrum. Since its inception, ARM has migrated over a long meaningful road map starting from v4T ARM7TDMI to v7 Cortex series of architectures achieving many strong milestones in between. It is currently the new era of feature rich ARM Cortex series architectures truly empowering the embedded computing world.

In order to provide a wide coverage of different application domains, addressing their specific requirements, ARM core is evolved into architecture version7 which has three different profiles: the application profile, real time profile and microcontroller profile. Architecture v7 should not be confused with ARM7 which has been explained before under architecture v4.

Cortex A series of architectures are multicores with power efficiency and high performance. Every Cortex – A implementation is intended for highest performance at ultralow power design. It supports with, in-built memory management unit. Being influenced by multitasking OS system requirements, it has virtualization extensions and provides a trust zone for a safe and extensible system. It has enhanced Java support and provides a secure program execution environment. These architectures are typically designed for high end real time safety critical applications like automotive powertrain system. Some Cortex- A application products are smart phones, tablets, televisions and even high end computing servers.

Cortex R series of architectures are designed for deeply embedded real time multitasking applications. They have low interrupt latency and predictability features for real time needs. It provides memory protection for supervisory OS tasks being in privileged mode. It also provides tightly coupled memories for fast deterministic access. Typical application examples are: hard disk drive controller and base band controller for mobile applications and engine management unit where high performance and reliability at very low interrupt latency and determinism are critical requirements.

Cortex M series of architectures have v6-M as cortex M0, M0+ and M1 and v7-M with Cortex M3, M4 and other successors. This series of architectures developed for deeply embedded microcontroller profile, offer lowest gate count so smallest silicon area. These are flexible and powerful designs with completely predictable and deterministic interrupt handling capabilities by introducing the nested vector interrupt controller (NVIC). The small instruction sets support for high code density and simplified software development. Developers are able to achieve 32-bit performance at 8-bit price. The very low gate count of Cortex M0 facilitates its deployment in analog and mixed mode devices. Due to further demanding applications requiring even better energy efficiency, Cortex M0+ was designed with two stage pipeline and achieved high performance with very low dynamic power consumption, reduced branch shadow and reduced number of flash memory access. Cortex M1 was designed for implementation in FPGA. It is functionally a subset of Cortex M3 and runs ARM v6 instruction set with OS extension options. It has 32-bit AHB lite bus interface, separate tightly coupled memory interface and JTAG interface to facilitate debug options. It has three stage pipeline implementation and configurable NVIC for reducing interrupt latency.

The programming model of the Cortex-M4 processors has 18 working registers shown in below Figure. Thirteen of them are general purpose 32-bit registers, three have special uses and two stack pointers.

Which course should be opted in Engineering?

To all the students who are looking forward to take Engineering admission, and to their parents, we would like to give some suggestions about branch selection.

There is no doubt that every student’s first choice is Computer Science only.But, to bring awareness in students, about the enormous opportunities provided by electronics field and about its importance and to encourage them to choose Electronics field, is the main agenda of this blog post.

Why is there so much demand for Computer Science Engineering?

Due to the salaries and lifestyle provided by software industry, not only the students, their parents are also attracted to this field.

Nowadays situation has become such that, job means only software engineer job, engineering means only computer engineering, nothing else is considered good.

As lot of people compete for Software Engineering jobs, only few of them get proper development opportunities.Remaining candidates just end up doing maintenance & support kind of jobs with no proper career growth.

What is the importance of Electronics branch in Engineering?

Nowadays mobile phone has become the basic necessity of human life along with food, clothes and shelter.

We cant imagine life without smart phone.

We cant find a house without atleast one electronic device. There will be atleast a TV and a Set top box to say minimum.

How are these electronic devices made?

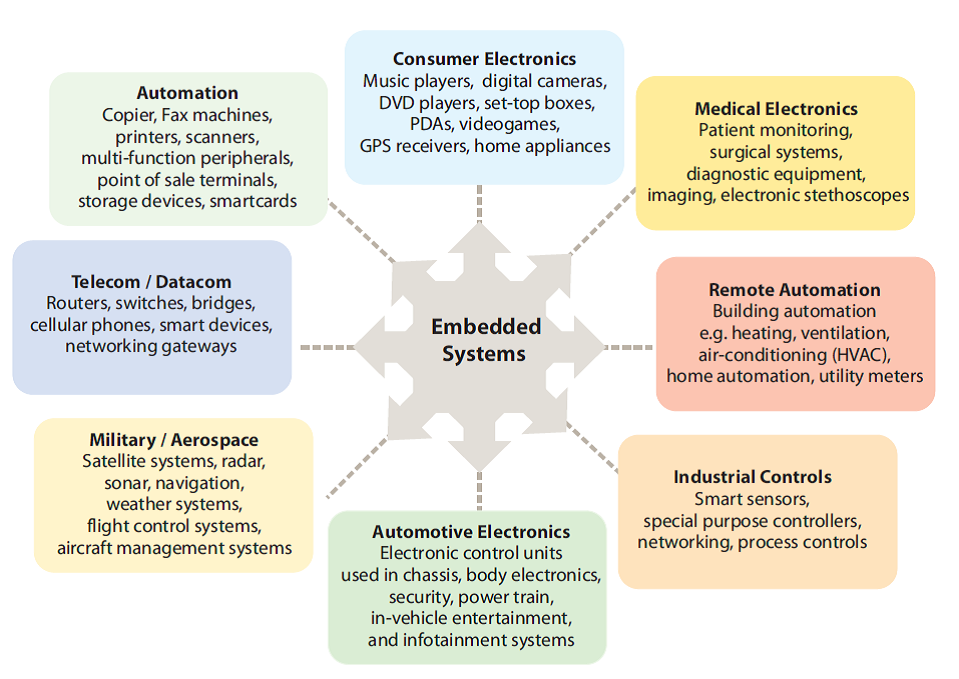

Electronic core fields like Embedded Systems & VLSI design and manufacturing fields are the ,main reason that we have all these devices.

Electronics field is no way inferior to Software field in terms of Job opportunities.

Most of the Electronics students are not aware of the opportunities provided by Electronics field, so they are either choosing Software field or moving on to higher studies etc.

As long as the situation is like this, we will have to import every electronics device that we need, from other countries like China or Japan.Make In India can never become reality.

What are the new courses added to Computer science branch, and what are the consequences of adding them?

In this academic year (2020-2021), 6 new engineering courses were added to the computer science department.

Those are

Most of the subjects in these courses are taken from the Computer Science Standard Curriculum.They should have been added as Specialisations in M.Tech instead of adding as new branches in B.Tech.

Because of adding these new branches in B.Tech, approximately 19000 new seats got added to Computer Science department alone.Because of the increased seats, most of the students will opt for Computers branches, which will effect core fields like Electronics Civil, Mechanical etc.

As these core fields get effected as no one is opting for them, the technology advancements in these fields will be hindered.If you see countries like China or Japan, they are technologically very advanced.

Why are these countries so developed? Because they give equal importance to all core fields, not just one field. That is why now they are in a stage to manufacture anything on their own and export it to other countries.

Because of the newly added seats in computer science department, all students will tend to choose Computer science branch only.

But we need to understand that increase of seats in a particular field does not mean increase in job opportunities. It means competition is increasing in that field.

One more thing is, technologies like Artificial Intelligence & Machine Learning are no doubt in demand, but these technologies have to be used in electronic devices only.So inorder to use these advanced technologies, we will require electronics basic knowledge.

Which means, Electronics field will continue to provide job opportunities and there will be demand for skilled resources.

So is it right that everyone chooses software field, leaving such an evergreen field like Electronics?

What I want to tell to students and their parents is,choose the field which provides good job opportunities, growth in career along with good salaries and job satisfaction. Choose Electronics Core field.

Let us together pledge to save the electronics core field branches like ECE & EEE. And make “Make In India” possible.

Buy a Community development board and apply the C programming skill to do good electronic projects by yourself without copying a single line of code from net/book/friends.

For Freshers, the resume should be mainly about their skill-set and academic details. Here are some tips about how to build your resume, section wise.

The Linux community Wolrd wide contains many students who are developing the code either out of Interest or as part of their academic projects.

But most of the colleges doesn’t have the proper environment suitable for Open Source Projects (Except for top most colleges like IITs/NITs). The students in those colleges don’t get any guidance on how to start with open source projects.

That is what we are implementing in our course, “Android for Embedded Systems” where we are going to make students do some real-time projects that are based on Linux / Android open source code.We also have academic projects for B.Tech / M.Tech students that are purely based on Linux / Android open source code.